[컴퓨터 구조] 논리 회로(2) - 조합 회로와 순서 회로

▶ 조합 회로

개념

- 입력과 출력을 가진 논리 게이트들의 집합이다.

- 출력 값은 입력 값 0과 1의 조합에 의해 결정된다.

- 기억능력이 없다는 것이 특징이고 게이트 자체가 기본이다.

- 반가산기, 전가산기, 디코더, 멀티플렉서 및 디멀티플렉서가 있다.

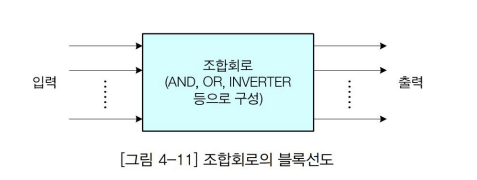

- 아래의 그림처럼 합회로가 입력을 받아 처리한 후 출력을 하는 형태로 되어있다.

어떠한 방법으로 조합회로를 설계할 수 있을까?

- 진리표 만들기

- 논리식으로 표현한 후 간소화(부울대수 법칙, 카르노맵 사용)하기 ( 논리식을 표현할 땐 SOP 방식을 주로 사용 )

- 논리식을 논리 회로도로 나타내기

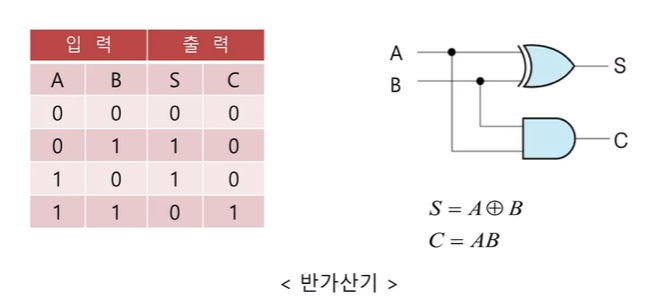

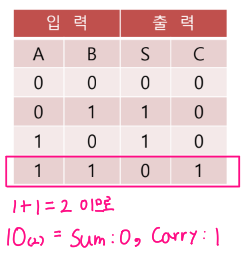

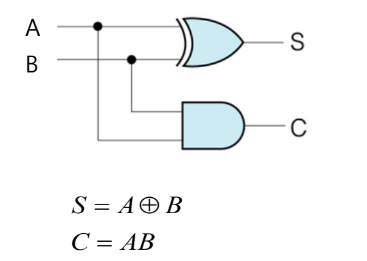

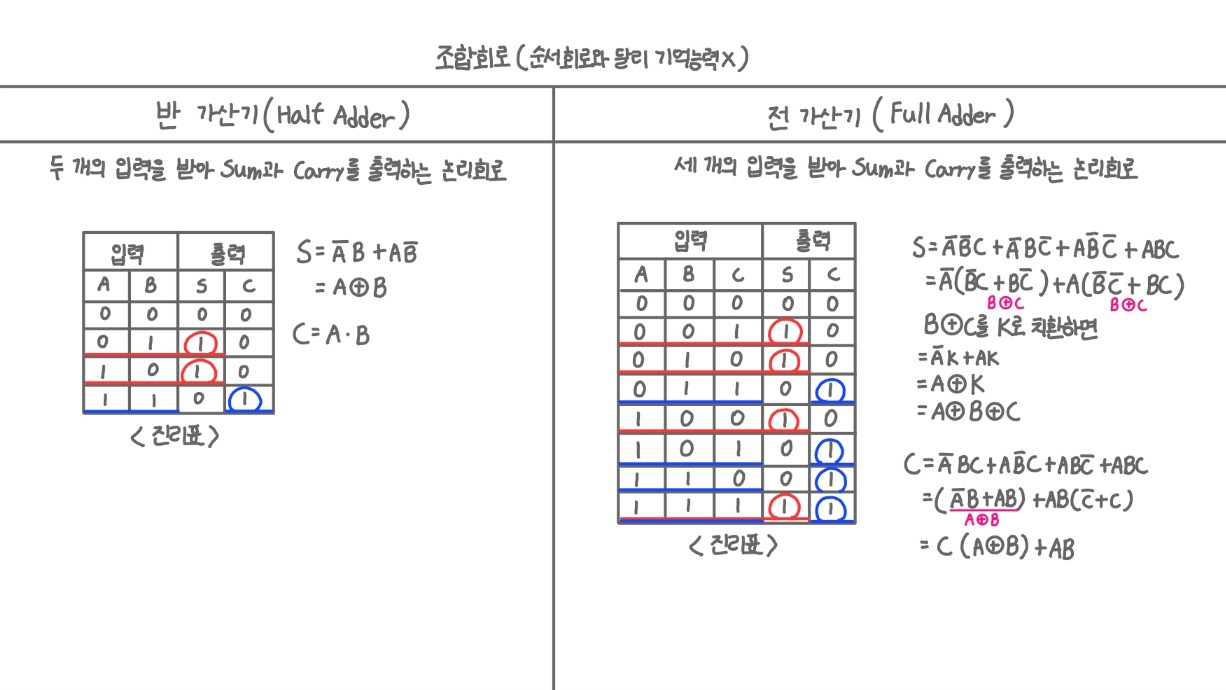

▷ 반가산기 (Half Adder)

- 두 개를 입력 받아 합(+연산)의 결과로 Carry(자리올림)와 합(sum)의 값을 구하는 조합회로

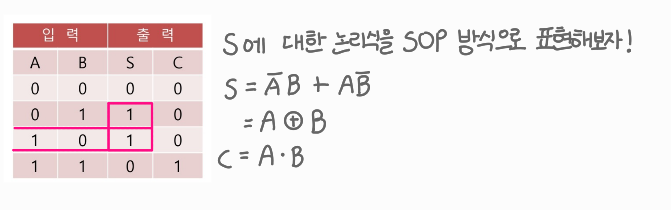

조합회로 설계

- 진리표 만들기

- 논리식으로 표현한 후 간소화

- 논리식을 논리 회로도로 나타내기

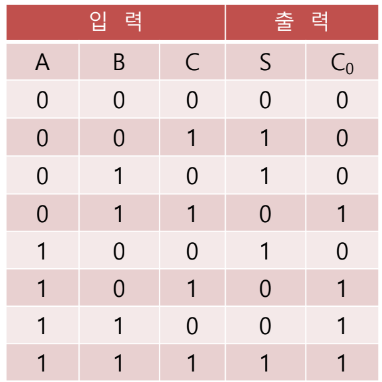

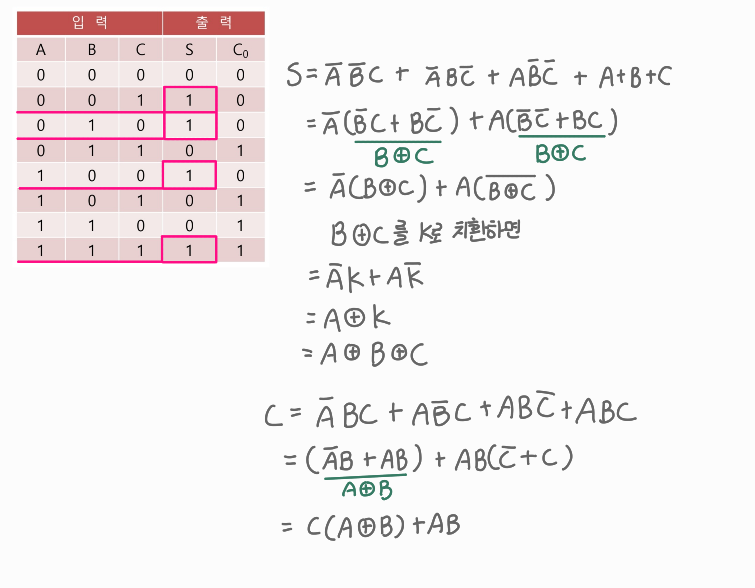

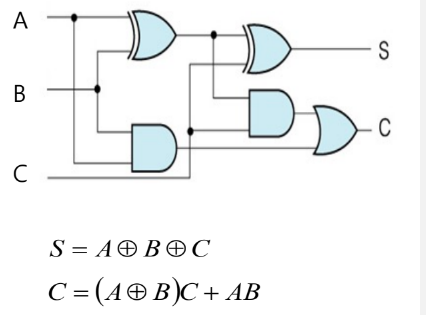

▷ 전가산기 (Full Adder)

- 세 개의 입력을 받아 Carry(자리올림)와 합(sum)의 값을 구하는 조합회로

조합회로 설계

- 진리표 만들기

- 논리식으로 표현한 후 간소화

- 논리식을 논리 회로도로 나타내기

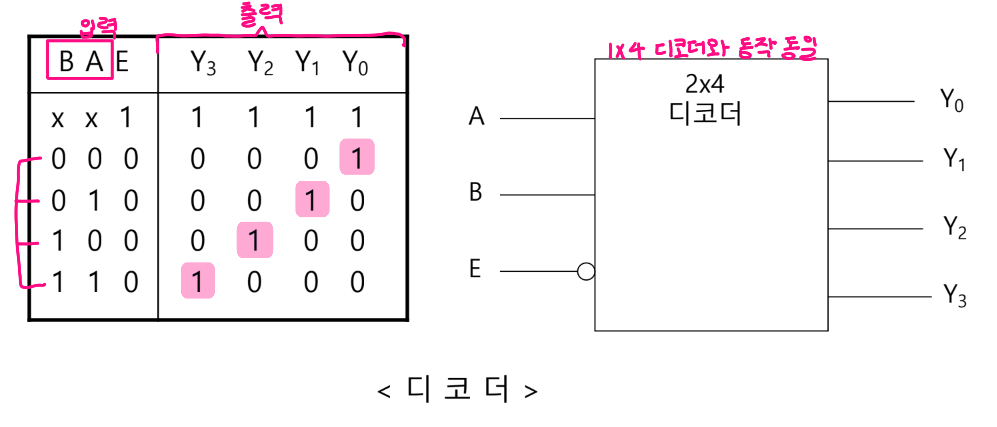

▷ 디코더

- n개의 입력으로 최대 n²개의 출력을 나타낼 수 있는 조합회로

- 출력중 하나는 1이되고 나머지 출력은 모두 0으로 표현

- RAM · ROM 같은 메모리 번지주소나 IR 해독할 때 사용

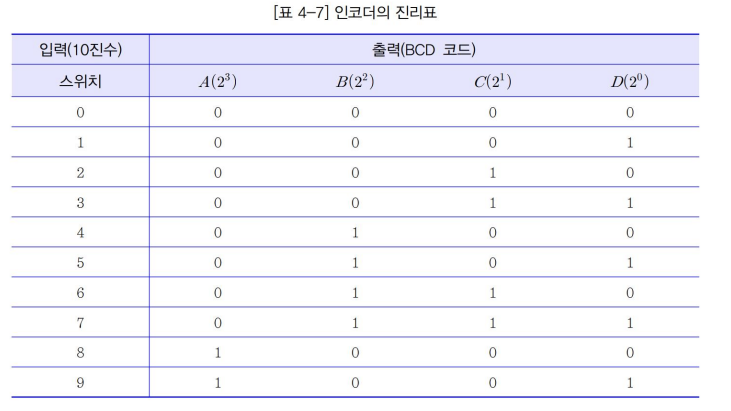

▷ 인코더

- 10진수나 8진수를 입력으로 받아들여 2진수나 BCD와 같은 코드로 변화시키는 회로

- ex. 탁상 계산기 키보드 인코더 : 9를 선택해서 누르면 이에 상응하는 4bit BCD 코드인 1001이 출력

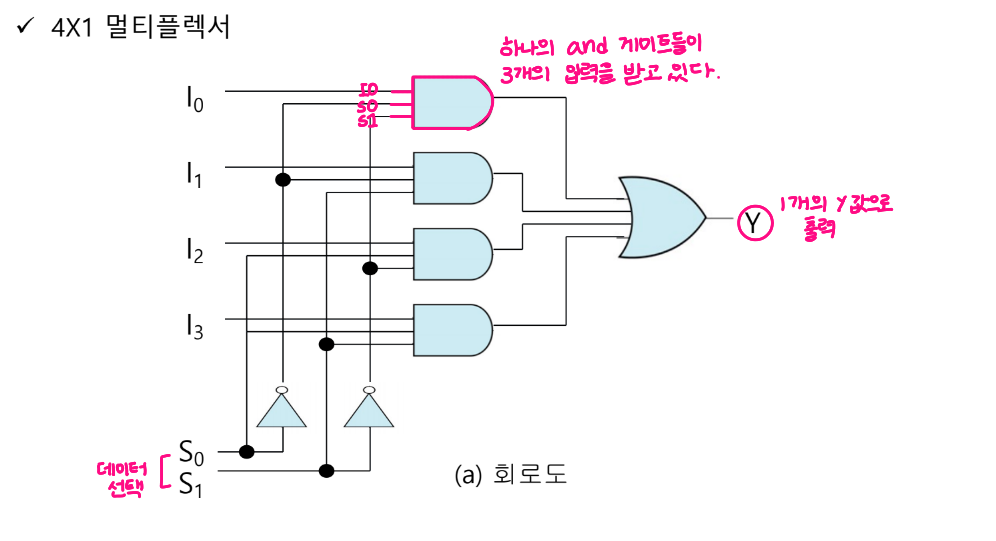

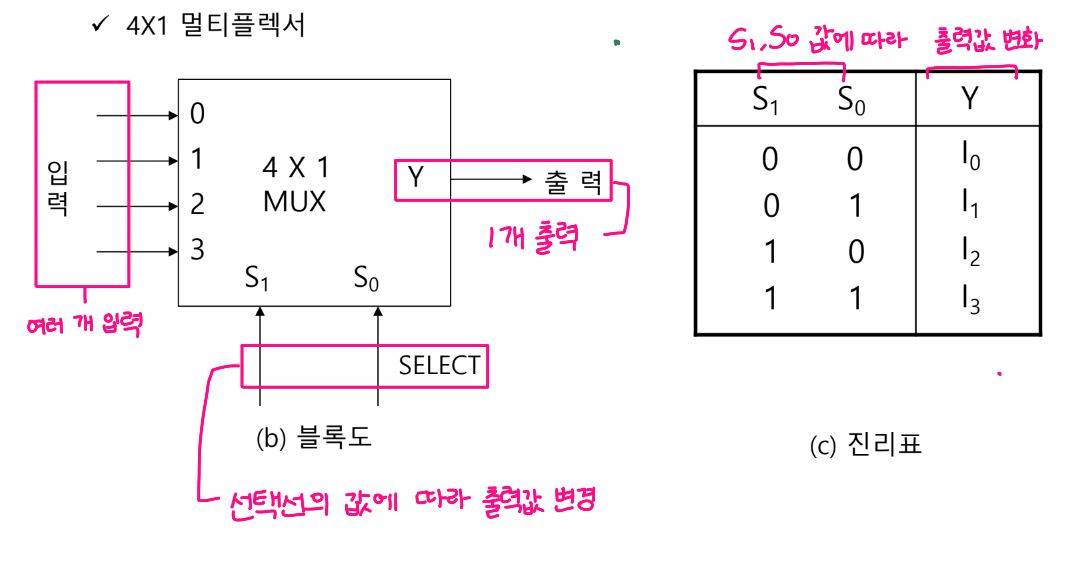

▷ 멀티플렉서

- 개념

- ①여러 개의 입력을 받아 ②선택선을 제어해서 ③데이터를 선택하여 값을 출력하는 조합회로

- 여러 개의 입력중에 하나를 선택하고, 2진 정보가 출력될 선을 결정하기 때문에 데이터 선택기라고 부른다.

4x1 멀티플렉서

- 4개의 데이터를 입력받아 1개의 data를 출력

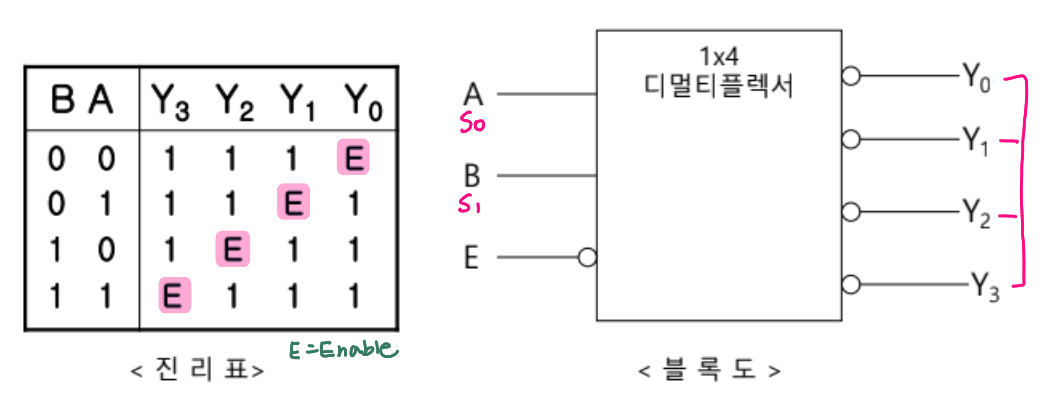

▷ 디멀티플렉서

- 개념

- ①1개의 입력을 받아 ②2ⁿ개의 출력 중 하나를 선택하여 ③정보를 내보내는 조합회로

- 제어 입력들의 값에 따라 출력중의 하나에 데이터 입력이 연결

- 데이터 분배기라고도 한다.

- 디코더와 디멀티플렉서의 특징 비교

- 디멀티플렉서의 선택 입력은 디코더에서의 인에이블 특징과 동일

- 2 X 4 디코더는 1 X 4 디멀티플렉서와 동일

( 즉, 인에이블 입력을갖는 디코더와 디멀티플렉서의 논리회로는 근본적으로 동일 )

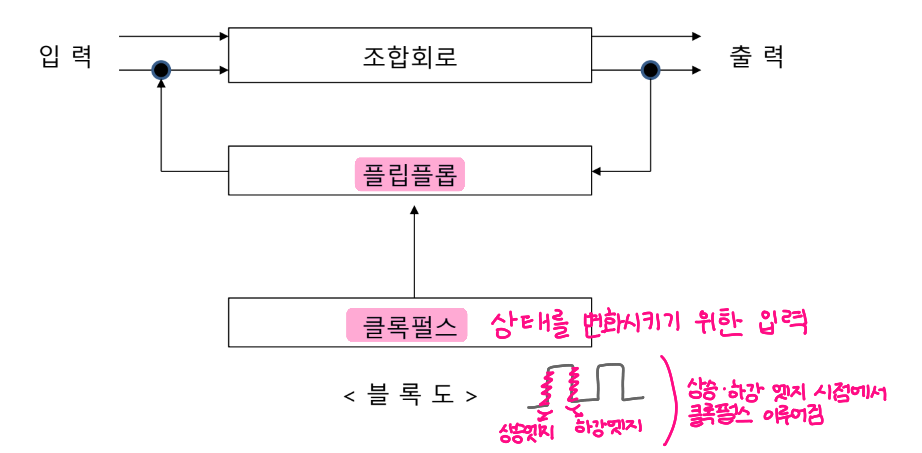

▶ 순서 회로

개념

- 조합 회로와 달리 ⭐정보의 이전 상태를 기억할 수 있는 게이트들의 집합

- 입력 값과 회로의 현재 상태에 따라 출력값이 결정되는 회로

- 플리플롭, 레지스터, 카운터가 있다.

▷ 플리플롭

- 1개의 비트 대한 정보를 기억하는 기억소자이다.

- 상태를 변화시키기 위한 입력( 클록펄스 )가 있을 때까지 상태를 유지

- 플리플롭을 조합하여 레지스터와 카운터 등 구성한다.

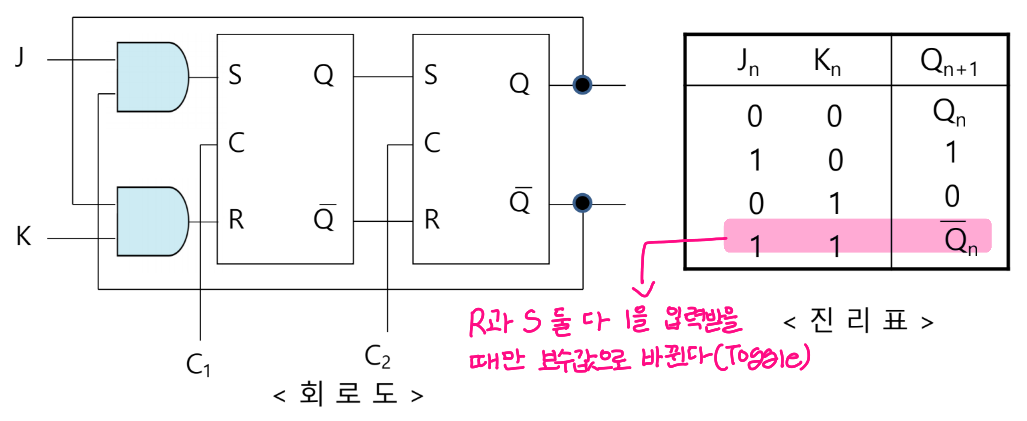

### ② JK 플리플롭 - RS 플리플롭의 결점을 보완하는 플리플롭( R과 S가 동시에 1이 되는 경우를 허용 ) - R과 S의 입력에 이전 상태 출력을 AND하여 처리한다. - RS 플리플롭 + T 플리플롭

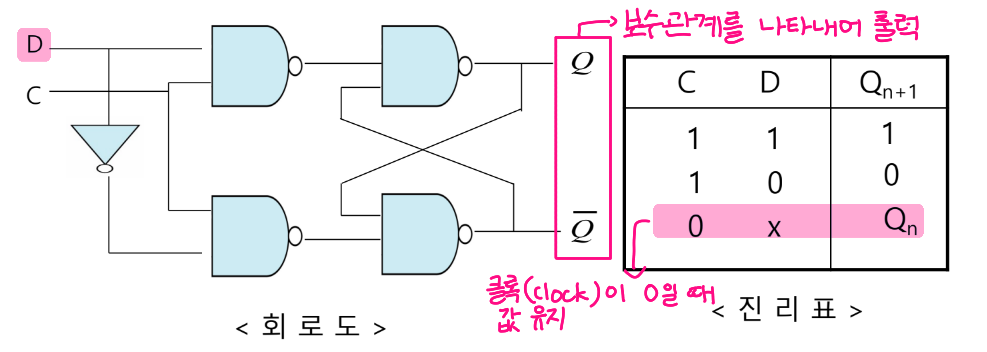

### ③ D 플리플롭 - D(데이터), Clk(클럭) 두 입력을 갖는, 가장 간단한 플립플롭 - 입력 D를 그대로 출력한다. - RS 플리플롭 회로에 NOT 게이트를 연결해서 회로를 변형한 것을 말한다. - 정보를 일시 유지하는 래치 회로나 시프트 레지스터 등에 쓰인다. (제일 많이 사용)

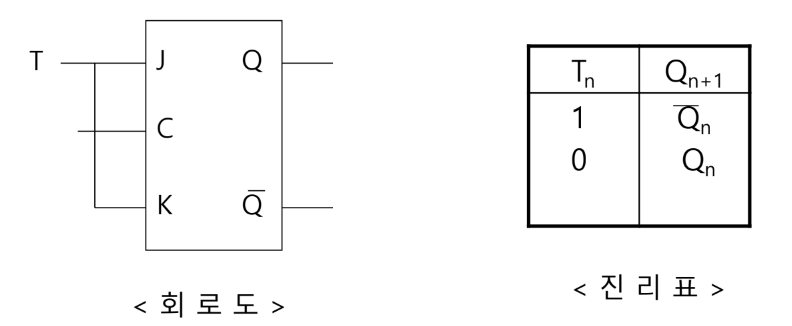

### ④ T 플리플롭 - J와 K를 연결해서 회로를 변형한 것으로 입력 신호(clock)가 들어올 때마다 출력 신호의 상태(플리플롭의 값)가 바뀌는 플리플롭 - 입력 단자가 T 하나이다. - 보수 플리플롭, Toggle 플리플롭이라고도 불린다.

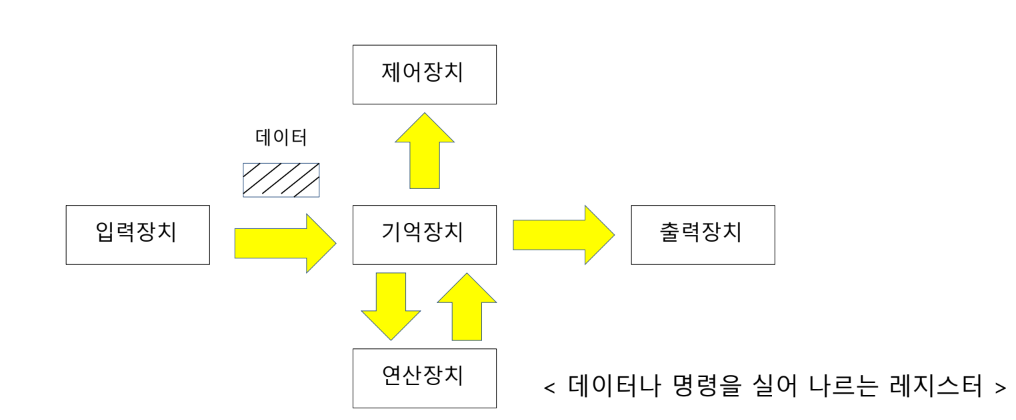

## ▷ 레지스터 - 레지스터는 플리플롭 회로를 여러 개 접속 시켜서 구현한다. - 여러 비트의 데이터를 일시적으로 기억시켜 필요할 때마다 인출 - 장치와 장치는 레지스터를 통해 데이터를 옮긴다. (직접소통x)

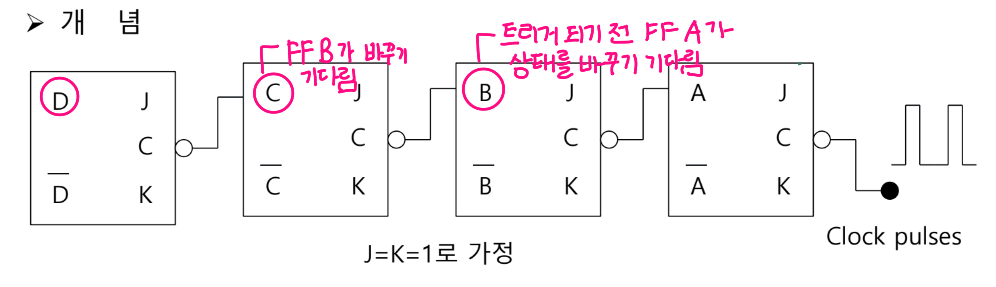

## ▷ 카운터 - 클록펄스의 수를 카운터해주는 역할을 수행한다. - 특징 : FF(플리플롭)의 수가 n개면 2ⁿ개의 독립된 수 표현이 가능하다.

---

# 🔖정리

---

# 📎참조 - 『 성결대학교 김자원 교수님 』 - 컴퓨터 구조 (2023) - 『 컴퓨터구조(제5판) 』 - 복두 출판사 - http://www.ktword.co.kr/test/view/view.php?m_temp1=4712 - https://blog.naver.com/PostView.naver?blogId=asd7979&logNo=30111607761

댓글남기기